Laporan Akhir 1

Laporan Akhir 1Gerbang Logika Dasar

1. Jurnal [kembali]

2. Alat dan Bahan [kembali]

Gambar 1.1 DL2203C Module D’Lorenzo

Gambar 1.2 DL2203S Module D’Lorenzo

Gambar 1.3 Jumper

Alat yang di gunakan :

3. Rangkaian Simulasi [kembali]

4. Prinsip Kerja Rangkaian [kembali]

Pada rangkaian diatas terdapat beberapa gerbang logika yang digunakan. Masing masing gerbang logika memiliki prinsip kerja yang berbeda.

- Gerbang NOT

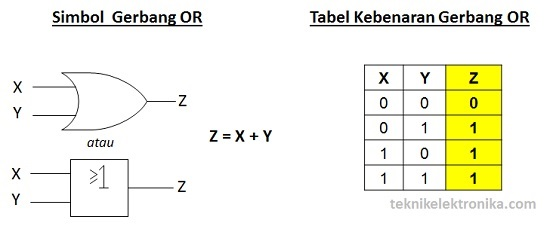

- Gerbang OR

Pada saat melakukan percobaan pada proteus, dengan input B0 dan B1. Sesuai dengan prinsip gerbang yang sudah dijelaskan diatas,

Sebagai Contoh Input B0 dan B1:

- B0 = 1 (HIGH)

- B1 = 0 (LOW)

Gerbang U1 (NOT):

- Input: B1 (0)

- Output: NOT B1 = 1

- Fungsi: Membalikkan sinyal input, jadi jika inputnya 0, outputnya 1.

Gerbang U2 (AND):

- Input: B0 (1) AND B1 (0)

- Output: 0

- Fungsi: Gerbang AND hanya menghasilkan 1 jika kedua inputnya adalah 1.

Gerbang U3 (OR):

- Input: B0 (1) OR B1 (0)

- Output: 1

- Fungsi: Gerbang OR menghasilkan 1 jika salah satu atau kedua inputnya 1.

Gerbang U4 (NAND):

- Input: B0 (1) NAND B1 (0)

- Output: 1

- Fungsi: Gerbang NAND menghasilkan kebalikan dari AND, yaitu 1 kecuali jika kedua inputnya 1.

Gerbang U5 (NOR):

- Input: B0 (1) NOR B1 (0)

- Output: 0

- Fungsi: Gerbang NOR menghasilkan kebalikan dari OR, yaitu 1 hanya jika kedua inputnya 0.

Gerbang U6 (XOR):

- Input: B0 (1) XOR B1 (0)

- Output: 1

- Fungsi: Gerbang XOR menghasilkan 1 jika inputnya berbeda.

Gerbang U7 (XNOR):

- Input: B0 (1) XNOR B1 (0)

- Output: 0

- Fungsi: Gerbang XNOR menghasilkan kebalikan dari XOR, yaitu 1 jika kedua inputnya sama.

5. Video Rangkaian [kembali]

6. Analisa [kembali]

1. Analisa masing-masing output H1 dan H2 ketika variasi A,B,C,D pada percobaan 1b!

Jawab:

H1 = (B ⊕ D) ∨ (A ∧ ¬C ∧ D)

H2 = (B ⊕ D) ∨ (A ∧ ¬B ∧ C)

7. Link Download [kembali]

Komentar

Posting Komentar