Fig 8.21

1. Pendahuluan [kembali]

Dalam dunia sistem digital, perangkat logika seperti demultiplexer dan decoder memainkan peran penting dalam proses pemilihan data, pengendalian jalur logika, serta pengubahan sinyal dari satu bentuk ke bentuk lainnya. Keduanya digunakan secara luas dalam sistem komunikasi digital, unit kontrol, dan aplikasi mikrokontroler.

Demultiplexer (Demux) adalah rangkaian logika yang berfungsi untuk menyalurkan satu input data ke salah satu dari beberapa output, tergantung pada kombinasi sinyal selektor (select lines). Dalam praktiknya, demux digunakan untuk menyalurkan data tunggal ke beberapa tujuan, seperti dalam sistem distribusi data, rangkaian kendali, atau interkoneksi bus data.

Sementara itu, decoder adalah rangkaian logika yang digunakan untuk mengubah data biner menjadi representasi output yang lebih kompleks atau terpisah. Decoder membaca sinyal input biner dan mengaktifkan satu dari banyak output yang sesuai. Salah satu contoh umum dari decoder adalah BCD to decimal decoder, yang mengubah angka biner menjadi format desimal agar bisa ditampilkan pada display.

Pemahaman mengenai prinsip kerja, struktur, dan implementasi dari demultiplexer dan decoder sangat penting dalam perancangan sistem digital yang efisien dan dapat diandalkan. Melalui praktikum atau simulasi ini, mahasiswa diharapkan dapat mengenali fungsi, simbol, serta aplikasi nyata dari kedua jenis rangkaian tersebut.

2. Tujuan [kembali]

- Mempelajari prinsip kerja BCD Adder, termasuk cara menangani hasil penjumlahan yang tidak valid dalam format BCD.

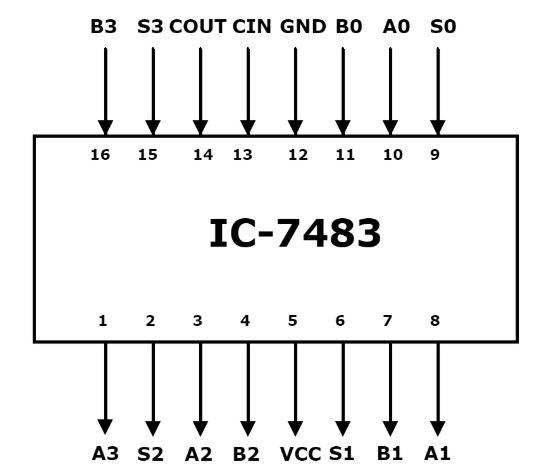

- Mendesain dan mensimulasikan rangkaian BCD Adder menggunakan IC 7483 (4-bit binary adder) serta logika koreksi penjumlahan (add-6) agar hasil tetap dalam format BCD yang valid.

- Mengidentifikasi kondisi overflow (hasil > 9) dari hasil penjumlahan dua digit BCD, dan menerapkan koreksi yang tepat secara logika.

- Menggunakan perangkat lunak Proteus untuk memodelkan dan mensimulasikan rangkaian BCD Adder secara visual dan interaktif.

- Mengembangkan keterampilan merancang sistem aritmatika digital, khususnya dalam penerapan logika kombinasi untuk pengolahan angka desimal

- IC 7483

- Gerbang AND

- Gerbang OR

Jenis kedua adalah gerbang OR. Sama seperti gerbang sebelumnya, gerbang ini juga memerlukan dua input untuk menghasilkan satu output. Gerbang OR ini akan menghasilkan output 1 jika semua atau salah satu input merupakan bilangan biner 1. Sedangkan output akan menghasilkan 0 jika semua inputnya adalah bilangan biner 0.

- NOT

- NOR

4. Dasar Teori [kembali]

Demultiplexer (DEMUX)

Sebuah Demultiplexer, sering disingkat DEMUX, adalah rangkaian logika kombinasional yang berfungsi sebagai "distributor" data. Rangkaian ini memiliki satu jalur input data, n jalur input pemilih (select lines), dan 2^n jalur output. Tugas utamanya adalah menyalurkan atau merutekan informasi dari satu jalur input ke salah satu dari banyak jalur output yang tersedia. Jalur output mana yang akan menerima data ditentukan oleh kombinasi biner dari sinyal pada jalur pemilih.

Sebagai contoh,

DEMUX 1-ke-4 yang ditunjukkan pada Gambar 8.18(a) memiliki satu jalur input, dua jalur pemilih (A dan B), dan empat jalur output (D0 hingga D3). Berdasarkan tabel kebenaran pada Gambar 8.18(b), jika input data diberi logika '1', maka:

Saat A=0 dan B=0, hanya output

D0 yang akan bernilai '1'.

Saat A=0 dan B=1, hanya output

D1 yang akan bernilai '1'.

Dan seterusnya untuk kombinasi lainnya

Decoder

Decoder adalah rangkaian kombinasional yang berfungsi untuk "menerjemahkan" atau "mendekode" informasi. Ia menerima n jalur input dan menghasilkan hingga 2^n jalur output yang unik. Setiap kombinasi input akan mengaktifkan salah satu dari jalur output. Decoder dapat dianggap sebagai kasus khusus dari demultiplexer yang tidak memiliki jalur input data.

Cara Kerja Decoder

Untuk memahami cara kerjanya, perhatikan

decoder 3-ke-8 pada Gambar 8.20. Decoder ini memiliki tiga input (A, B, C) dan delapan output (D0 hingga D7). Dari diagram logika dan tabel kebenarannya, dapat dilihat bahwa untuk setiap kombinasi input biner, hanya satu output yang akan aktif (berlogika '1'). Setiap output ini merepresentasikan sebuah minterm dari variabel input:

D0 aktif saat ABC=000, merepresentasikan minterm ABC.

D1 aktif saat ABC=001, merepresentasikan minterm ABC.

Dan seterusnya hingga D7 yang merepresentasikan minterm ABC.

Aplikasi dan Implementasi Decoder

Decoder memiliki berbagai aplikasi praktis dalam sistem digital, terutama dalam implementasi fungsi logika dan pembuatan rangkaian yang lebih kompleks.

1. Implementasi Fungsi Boolean

Decoder sangat berguna untuk mengimplementasikan fungsi Boolean secara langsung dari bentuk Sum of Products (penjumlahan minterm). Caranya adalah dengan menggunakan decoder untuk menghasilkan semua minterm yang diperlukan, lalu menggunakan gerbang OR eksternal untuk menjumlahkan minterm-minterm tersebut.

Sebagai contoh (Example 8.6), untuk mengimplementasikan rangkaian Full Adder, kita perlu dua fungsi:

SUM = Σ(1,2,4,7)

CARRY () = Σ(3,5,6,7)

Implementasinya menggunakan decoder 3-ke-8 seperti pada Gambar 8.22:

Untuk output SUM: Output decoder nomor 1, 2, 4, dan 7 dihubungkan ke input sebuah gerbang OR.

Untuk output CARRY: Output decoder nomor 3, 5, 6, dan 7 dihubungkan ke input gerbang OR yang lain.

Teknik Optimasi: Jika sebuah fungsi memiliki jumlah minterm yang banyak (lebih dari setengah total kemungkinan, atau >2n−1), akan lebih efisien untuk mengimplementasikan fungsi komplemennya (F) yang memiliki lebih sedikit minterm, lalu hasilnya dihubungkan ke gerbang NOR. Contohnya pada Example 8.7, fungsi memiliki 5 minterm. Komplemennya, , hanya memiliki 3 minterm. Maka, lebih efisien untuk menghubungkan output decoder 1, 3, dan 4 ke gerbang NOR 3-input.

2. Cascading Decoder (Membuat Decoder Lebih Besar)

Seringkali kita membutuhkan decoder yang lebih besar dari yang tersedia dalam satu IC. Untuk mengatasi ini, beberapa decoder kecil dapat dihubungkan secara berjenjang (cascade) untuk membentuk decoder yang lebih besar.

Contohnya (Example 8.8) adalah membuat decoder 4-ke-16 dari dua buah decoder 3-ke-8 (lihat Gambar 8.24). Langkah-langkahnya adalah:

Hubungkan Input Data: Tiga bit input yang kurang signifikan (A, B, C) dari input 4-bit dihubungkan secara paralel ke input kedua decoder 3-ke-8.

Gunakan Input Sisa sebagai Enable: Bit input yang paling signifikan (D) digunakan untuk mengontrol pin ENABLE pada kedua decoder. Bit D dihubungkan ke pin ENABLE salah satu decoder, dan D (melalui gerbang NOT/inverter) dihubungkan ke pin ENABLE decoder lainnya.

Hasil: Dengan cara ini, saat D=0, decoder pertama aktif dan menghasilkan output D0 hingga D7. Saat D=1, decoder kedua aktif dan menghasilkan output D8 hingga D15.

5. Percobaan [kembali]

a). Prosedur

- Mempersiapkan Alat beserta Bahan seperti yang telah tertera pada Sub Bab Alat dan Bahan di atas

- Merangkai Rangkaian

- Pada Rangkaian disambungkan input berupa gelombang pulsa agar dapat melihat bagaimana perbedaan respons gelombang input dan outputnya.

- Amatilah nilai input dan output dengan menyesuaikannya dengan rumus yang ada,

b). Rangkaian simulasi dan Prinsip kerja

c). Video simulasi

6. Download File [kembali]

- Rangkaian 8.21 [download]

Komentar

Posting Komentar